UNIT-I Junction Diode P-N Theory of P-N Junction :-Combining ptype S.C. f. ntype S.C. forms PNM. -> Connecting di (two) electrodos' to the PN SN forms PN m. diode. B.G.G. C. D. B. B. D. Donaston Electron Acceptorian Hole Diffusion of electron Deffusion of hole The donot ion is indicated Schematically by a plus Sign below, after this impurity atom "donates" an electron, it becomes Post-five Pon. the acceptor con is indicated by a minus Sign be cause, after this atom "accepts" on electron, "it becomes a negative in, when PAN type are arbining together by an appropriate Scherre like Ion implantation of diffusion. Properly formed PN on will be having ptype on one side for type on the prother side , P-type S.c. have accepts Tars of Choriean are holes (Positively draged) ાત્ત dong fn-type 11 .4 и . electors

According to Mass. Actin Law for Nortype

$$P_n N_n = n!^n$$

$\therefore \boxed{N_0 \equiv \frac{m_1^n}{P_n}}$

$P_n Type Sic:-

$P + N_p = n + NA$

$U = np \Rightarrow Constraints of free electrons

$P_p \Rightarrow$  jobs

$N_n \Rightarrow$  " durch atom.

$TXr P_n type Sic N_0 (Dord, Apping) = 0. Here

$P_p = np + NA$

$\therefore P_p \Rightarrow np = NA^m P_p$

$\therefore P_p \Rightarrow p_p = NA^m P_p$

$\therefore P_p \Rightarrow p_p = NA^m P_p$

$\therefore P_p \Rightarrow np^* \Rightarrow \boxed{NA^m = \frac{m_1^n}{N_p}}$

$Drift welself 1:-

$-A \ charged partities results when the charge Caster differs to statch

three courses under the influence of an applied charge with it a additional

differs when the influence of an applied charge with it is a additional

differ welself Va'

$durft welself Va''$

$durft welself I:-

$A \ charged partitional to the chart child  $\Rightarrow V_{d=p+e}$

$when \mu \to M_p \ type Va''$

$durft welself I:-

$Drift welself I:-$

$Drift$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$

. .

•

••••

•

• •.

• •

:

Ξ.

5

•

10 There will be difference in the Concentration of those will be a Concentration gradient of holes from p to N side & Concentration gradient of electrons from N to pside. whenever there is a Concentration gradient then the Carriers holes of electrons will try to flow from a higher Concentration region to laver Concentration region Just like whenever there is a pressure C différence in the mater level b/w two places then higher pressure water will flow down to place where pressure of mater is low, Similarly because of difference in concentration, hales will Stort moving from ptype to Ntype. This procen is called diffusion. Here these holes will be crossing In from left side to right side Right nide to left side of electrons will be .2 This procens is diffusion. Diffusion of holes of electrons will take place whenever we bring PN on together, As this Cassiels, holes from left side Cross over to the right side electrons from fight side Cross oues to the left side then there will be reamberation of charge because holes will be reambined by free electrons. I electrons will be reambine with holes. At the instant of pn-In formation, the free electrons near the In in the n region begin to diffuse a cross they in site the pregion where they combine with holes near the M. The result is that n region Lores free electrons as they diffuse into the m. randoman Scanned by CamScanner

This creates a Layer of positive charges (perstavalant Ears) near the m. As the electrons move across the on, the pregran loses holes as the electrons and holes Combine. The result is That There is a layer of negative charges (trivalent Pars) near the on. These here layers of postive of negotive charges form the depleton region (of depletion layor). The term depletion is due to the fact that near the m, the region is depleted (I.e. emptied) of charge carries (Analchart and holes) due to diffusion acros the on. It may be noted that depletion layer is formed very quickly and is very thin Compared to the n neglar cond-the Pregion. For clarity, the width of the depletion layer is Shown enaggerated.  $\Theta$ 26+ M 6 6 GIADIGE ဓိဓိဓုမျှမျှမျှမျ်းစ်စေါ် ê ê ê e e e e ů) Electric Depletion Region -Depletion 166-31 P  $\mathcal{N}$ Layes Space chalge fign ÐĐ Tronsition Region Ð  $\ominus$ (d)(È Θ Unneutralised crocyes The thickness of depletioning in an Covered charges that potential difference 10 Acm = 10 - 6 m = 1 micron aune

Once pri in is formed and depletion Layer created, the diffusions: free elections Stops. In other words, the depletion region acts as a barrier to the further E movement of free elections a cross the In. The postive and negative charges Set up an electric field. This is Shown in fig. The electric field is a barrier to the free electrons in the n-region There exists a potential difference across the depletion layer and is Called barrier potential (Vo). The barrier potential of a pri jri depends upon Several factors including the type of Seni Conductor material, the amount of doping and temp. The typical barrier potential is approximately ; . + U 5 For Silica, Vo=0.7V, For Germonium, Vo=0.3V Conductivit !!-Cartin · Va > deftuelousy · Distoral = time x velocity.  $\therefore t = \frac{L}{V_1}$ The total amount of charge in whit volume = ng The total charge in the Conductor, Q = ng × (volume) = ng A2 ÷ : V= ATRO the state . The current,  $I = \frac{Q}{t} = \frac{nqAL}{L/Vd} = n_q A V_d = nqA \mu G$ ligt T(amont) Current density  $J = \frac{T}{A} = nq\mu E$ , this is the Current per anit density of Caro-de Cheon we can replace the quantity nay the by a Constant on, Conductivity with on = ng 14

J=0E · , R=1 : DIZ OBRV=IR => I=GV -> Grductivity ( -> resistourly Electrical Properties of Servi Conductor Materials Conductivity!. we know that, or = ngite. ->. O..... Carduction in Conductors is due to electors where as, Conduction in Sic due to two types of charge Callers, "inc. electrons and holes on the basis of eqn . O, the Conductivity of a of a S.C material can be obtained as In = ng/ Kn -> due to electrons ~p=partep -> due to holes J= Enter == ngkn+pakp = a (nkn+pkp) Hn -> mobility of free electrons Mp -> Nobility of holes or -> charge of a Camer M, P -> Electron, Lale Concentrations

Drift Current It a battery is Gonected acros a S.C bas as 3 how intig. Total Curret, I = In + Ip Elictron - Drift to to to to Hole Drift dector flow Holes plan -111 Batter -then electrons being negative charged particles moves towards the positive terminal of the battery and holes being positive charged particles moves towards the negative terminal of the battery. Hence, the movement (drift) of holes and Electrons contribute to cledric current. This is called as drift currente. Diffusion Current Let us Gassider a S.C bas in which the concentration of change

Carlier (electrons of holes) in one region is greater then the other region of the SIC

> High Chalge low charge Grantration Concertration Diffusion Current Diffusion Current DistonCe (X)

Because of charge gradient, the charge cassies in the high Gradienting region move towards the law Concentration region. This process is alled different.

Scanned by CamScanner

and thus produced electric current is called as diffusion current. The Current density due to thes diffusion is proportional to the Calles dersify gradient. Current density due to hale deffusion is given by ie,  $Jp a \frac{dp}{dn}$  :  $\frac{dp}{dn} = Concertration gradient$ :  $\frac{dp}{dn} = Concertratient$ :  $\frac{dp}{dn} = Concertratient$  dp = Slope of the groph of Current density due to electron d' Husim is given by  $J_n = toy D_n \frac{dn}{dt}$ where Dp -> Hole diffusion Grotoret (m²(s) Dn -> Electron deffusion Constant (m²/s) dP -> Density gradient of holes. dn ) Density gradient of electrons Dp, Dn ale deffusion anstants given by Einsteins Relation shipe up - roltage equivalent often  $\frac{Dp}{\mu p} = \frac{Dn}{\mu n} = V_T = KT = \frac{KT}{9} = \frac{360}{11600} = \frac{26mV}{11600}$ K- 8.62×10-5euler E→ 1.38×10-235/°F  $V_T = kT$ At room temp ise, at 27°C, T= 273+27 = 300°K  $V_T = KT = 8.62 \times 10^{-5} \times 300 = 0.026 V (at 300° E)$ Total Current: - total Current in as c may be pomble to have the currents Contributed by both charge gradient & electricitield thus the total current is given by Jn = ngikn E + 91 Dn dr Jp = ParkpE - a Dpdp

the second what

Scanned by CamScanner

8

Di Electrode Arrow Head Ovelicates PN In Diode:-Direction of Govential Diode whent when found Biased inction Cathode N-type P-type Metal Contacts Copper Connecting. leads (b) Symbol of P-N MDiode (a) Structure of p-n In Diode In electronics, the term bias refers to the use of d.c. voltage to establish Certain operating Conditions for an electronic deura. In relation to a PNIM. there are two bias Conditions (2) Reverse blasing (1) Forward blasing (1) Forward Biasing N (b) Circuit Symbol a, prim when the positive terrival of DC source & battery is Corrected to p-type and regative terriral of battery is connected to N-type S.C of a PN m dide, then the dide is said to be forward beared.

0 (25 operation -PN jn is F.B, the holes (positive charges) on the when the P-side are repelled from the fue terminal of the battery of are forced to move to wards the m Il by the electrons ("we charges) on the n-side are repetted from the '- ve terminal of the ballery & are driven towards the Because of their acquired every from the voltage barre some of the holes of electors enter the depletion Loyee of recombine themselves. An a result, both the depletion region width of potential barrier reduces. when the bias voltage is progressively increased beyond the barrier potertial (For si vo=0.74, Forge Vo=0.34) then the electron from the N-Node Cross the PN on and are attracted by the five terminal of battery on the P-ride. 11 y the holes from the p-hide com the pron and all attracted by the '- we terminal of battery on the N-Mide -Both there charge Carrier flaw Carstitutes a Majdity Current V.0 =0 wa 107 A wardit Couldent JOL Kurt NOEnternel 00 600 Ð Θ Ectoral Field . [0]@i@.@.@ 000

(2) Reverse Biastry (b) Circuit Syrbol (a) PNM when the positive terminal of DC source & battery is Connected to N type Sic & negative terrival of battery is corrected to Ptype Sic of a PN IN as shown in fig. then the In is raid to be Reverse Biased, when the PNON is reverse biased the holes in p-side ale operation :attracted towards 'i've terminal of the bottery. Electrons on the N-sede are attracted towards the terminal of the battery. This action increases the depletion region and balles potently as shown in figure. The Increase in barrier potential prevents the flow of Magority Carriels. However, there are some electrons (Mirenty Camers) on the P-Nide & boles (Minority Carliers) on the N-Nide se The barnier potential helps these Mindity Callels to Cross the M. & a small magnitude of <u>reverse current</u> I. flang alron the M. This aument is Called reverse Saturation Current.

12 (2) 2 10 60 6-0 Esternal Auld 13 0000000000 No Enternal field 000000000 0.0. 99 00 0 0 ) Holes Volt - Ampere Characteristics of Print V-I characteristics of a prim is the curve b/w voltage across the m of the circuit current. we can know the behavior of a diode by in a circuit by U-I cheracteristics. . Usually, Voltage is taken along x-avis of current along y-anis. R mA PN K-> Switch OFF - open circuit(oc) -0 - Chort circuit(5.0) -chord cke K ON

PN ON dlade The V-I characteristics Can be Studied under three Blass- application of enterral Voltage about the two (1) Zero external voltage (No blas) temtrals I flynd) (2) forward bias Cume Ĵ Reverse bias (3) ma o オズロー y B 200 r Es Bar 150 100 · voltage Current 550 15 10 0 > VF (VOLTS) VR (VOLTS) & 11 0.2 0.3 0.4 05 0.1 0 Do thusan x-ann Net annes 100 ige across diode 200 Break Down 300 voltage 4.00 Poto Ip(pA) (No bias) under steady Zero external voltage i- when the external voltage is 'O'. extens C open at 'K'. The potential barrier at the In does not permet current flow. .. The cke current is zero, Indicated by pt "O" in fig. Forward bias: - when CKt is F.B, the potential baselies is reduced (2) of at some forward voltage (0.7 v for SI of 0.3 v for Ge) the current starts flowing in the clit. Above the forward voltage the current increases with increase in applied voltage. Thus observe Curve 'OB' as shown in fig . The first region OA' the current pris very slady of the curve is non-linear, Hensonce the external voltage exceeds the potential balling voltage the PN on behavis like on address

The majority (role) current Type is gluen by

Type (3) = T - Type (3) = 1)X

unitigative that, if PA Didde Current

when a finance bien is applied to a drode, train are typected

from the P-Side Sorts the N-Add-

The hole Concadention is providerial is gluen by

$$p_n(x) = P_{n0} + P_n(x) = -n(1+p) - 3$$

where  $P_{n0} = Theoret equilibrium Concadention

where  $P_{n0} = Theoret equilibrium Concadention

$Lp = 2d frain Uright of View In N-maleical.

$Lp = 2d frain Uright of View In N-maleical.

$L = 2d fraine known the junction where Concadention

$d = destance known the junction where Concadention

$d = destance known the junction where Concadention

$d = destance from the junction where Concadention

Hele Concadention of the junction of the concadention

$f_{n}(0) = P_{n}(0) - P_{n0} - - (9)$

$f_{n}(0) = P_{n}(0) - P_{n0} - - (9)$

$T = -y D p \frac{dE(x)}{dt}, A = (-p_{n}(b)) = P_{n0} + P_{n}(a) c^{-1}/dt_{n}$$$$$$$$$$$$$$$$$

$$P_{n}(x) = P_{n}(0) + P_{n}^{1}(0) e^{-x/lp}$$

$$\frac{d P_{n}(x)}{dx} = P_{n}0 + P_{n}^{1}(0) e^{-x/lp}$$

$$\frac{d P_{n}(x)}{dx} = P_{n}0 + P_{n}^{1}(0) e^{-x/lp}$$

$$\frac{d P_{n}(x)}{dx} = P_{n}0 + P_{n}^{1}(0) e^{-x/lp}$$

$$F_{n}(x) + A_{n} D_{p} P_{n}^{1}(0) \cdot e^{-t/p}$$

$$P_{n}(x) + A_{n} D_{p} P_{n}^{1}(0) \rightarrow e^{-t/p}$$

$$P_{n}(x) + A_{n} P_{n} D_{p} P_{n}^{1}(0) \rightarrow e^{-t/p}$$

$$P_{n}(x) + A_{n} P_{n} D_{p} P_{n}^{1}(0) \rightarrow e^{-t/p}$$

$$P_{n}(x) + A_{n} P_{n} P_{n} P_{n}^{1}(0) \rightarrow e^{-t/p}$$

$$P_{n}(x) + A_{n} P_{n} P_{n} P_{n}^{1}(x) + P_{n} P_{n}$$

.

с. 1

· · · · · · · · ·

H.

Scanned by CamScanner

Total diode current: The total diode current T at use is gran by-

$$I = T_{pn}(0) + T_{np}(0), \rightarrow (3)$$

When  $T_{pn}(0) = current Gaused by bala address N-rayin

$$T_{np}(0) = u + duds + p + rayin

the value of  $T_{pn}(0)$  Ga be Gatedisted by using  $e_{pn}(6)$   $f(e_{p}, two

$$T_{pn}(0) = \frac{h_{N} D_{P}}{L_{P}} \left( P_{n0} e^{U/v_{T}} - P_{n0} \right) \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P}}{L_{P}} \left( P_{n0} e^{U/v_{T}} - P_{n0} \right) \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P}}{L_{P}} \left( P_{n0} e^{U/v_{T}} - Q_{n} \right) \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P}}{L_{P}} \left( e^{U/v_{T}} - Q_{n} \right) \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P}}{L_{P}} \left( e^{U/v_{T}} - Q_{n} \right) \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P}}{L_{P}} \left( e^{U/v_{T}} - Q_{n} \right) \right)$$

$$G_{n} = \frac{f_{n}}{L_{P}} \left( e^{U/v_{T}} - Q_{n} \right) \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P}}{L_{P}} \left( e^{U/v_{T}} - Q_{n} \right) \right)$$

$$G_{n} = \frac{T = T_{0} \left( e^{U/v_{T}} - Q_{n} \right)}{L_{P}} \left( e^{U/v_{T}} - Q_{n} \right) \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P} P_{n0}}{L_{P}} + \frac{h_{N} D_{N} h_{P}}{L_{N}} \right) \left( e^{U/v_{T}} - Q_{n} \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P} P_{n0}}{L_{P}} + \frac{h_{N} D_{N} h_{P}}{L_{N}} \right) \left( e^{U/v_{T}} - Q_{n} \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P} P_{n0}}{L_{P}} + \frac{h_{N} D_{N} h_{P}}{L_{N}} \right) \left( e^{U/v_{T}} - Q_{n} \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P} P_{n0}}{L_{P}} + \frac{h_{N} D_{N} h_{P}}{L_{N}} \right) \left( e^{U/v_{T}} - Q_{n} \right)$$

$$T_{pn}(0) = \frac{h_{N} D_{P} P_{n0}}{L_{P}} + \frac{h_{N} D_{N} h_{P}}{L_{N}} \right) \left( e^{U/v_{T}} - Q_{n} \right)$$

$$T_{N} = \frac{h_{N} D_{P} P_{n0}}{L_{P}} + \frac{h_{N} D_{N} h_{P}}{L_{N}} \right) \left( e^{U/v_{T}} - Q_{n} \right)$$$$$$

The reverse Saturation Current: use know that Pro= Mer and Mpo= Min 7 Sub 13 + 19 in 12  $I_{0} = \begin{pmatrix} A_{q} D_{p} \begin{pmatrix} n_{p}^{2} \\ N_{p} \end{pmatrix} + A_{q} D_{n} \begin{pmatrix} n_{p}^{2} \\ \overline{N_{p}} \end{pmatrix} \\ - I_{p} \end{pmatrix}$ ND= Condition  $I_{O} = A_{QV} \left( \frac{D_{P}}{L_{P} N_{D}} + \frac{D_{n}}{L_{n} N_{A}} \right) m_{i}^{2}$ NA = Accepto -the walke (where mp2 = Aot3 are KT met = A ot B e VT where VGo = Voltage numerically equal to me forbiddens gop Evergy Eq. in election volt VT = Voltage equivalent of temp = T 11,600 limiting values of PN on diader. PN M well perform Sattstactorely anly i'f it is operated within Certain limiting values. (i) Manimum forward current: - The highest current under F.B Grdition - that Can flow through the junction. (1) Peak Invene witage (PIV)1- Max sevene voltage that Can be applied to the PNON. It vig across on exceeds privender R.B., on gets damaged. (11) Man, Power Roding :- It is the max, power that Can be dissipated at the M wetnast damaging the m. Power dissipation is the product of vottage across the IN - & current through the on

Ē Applications of PN on didus An ideal PN on diode has zero resistance when it is Infinite resistance when it is Due to this characteristic the diode finds a nounber of 4 applications as follows. (2) Switch in digital Logic circuits used in Computer (1) rectifiers in de pour supplies (3) clamping retroork used as dc restorer in TV receiver. (4) dipping circuits used as wave shaping circuits used in Corputers, radas, radio of TV receivers. (2) The Same PN Junction with different doping Concerts (5) demodulation (detection) Circuits fonds special applications as follows: (1) detectors (APD, PIN photo diade) in optiGL Communicat (2) Zever diodes in voltage regulater (3) Varactor diades in turing Sections of radio of TV reci (4) Light emilting deades in digital displays (5) LASER diodes in optical Communications (6) Tunnel diodes as a relaxation os cilletos at micro wave tre

18

Temperature Dependence of V-I characteristics of Tides:-The Boltzmann's equation of diode current is expressed as  $T = T \circ \left( e^{\sqrt{N_{T}}} \right) T = T_{o} \exp \left( \frac{1}{N_{T}} \right) - I_{T}^{T}$ where, I = diode current (positive when F.B.f.) Io = diode revene current at Temps. V = die de voltage (positive for F.B 4-regative to R.B) M=1 for Ge & 2 for si VT = I, a questity in volts dependent upon 1.600 T = temp of diode tr (°E) At room temp Say 22°C, T=295°K f VT = 0,02 5 volt. Thus  $I = I_0 \left( e^{A_0 V} - i \right), \text{ for } Ge$  $f = I = I_0 \left( e^{20^{\circ}} - 1 \right), for si$ where To is the reverse Saturation current at room temp. In is temp dependent. It Can be shown that it increases 7%. per'c for both Ge & Si. And it doubles for every 10° c rise intemp. Note: - Ge is more temp dependent than Si because its reverse current is approximately loss times Lasger.

Scanned with CamScanne

29

20 (I Ideal UN Practical - Resistance levels (Staticard Dyrange) gue repland F.B .) Forward resistance should be zero of In Ideal Case, Reverse resistance should be inflitte Dhacherel practice, no diode is an ideal diode because, neither it acts as a perfect conductor when F.B not it acts F. M-D Diterrities . AM as an insulator when it R.B. using water pilo So we an say that, in F.B, it offers. very . Small revestora (not exactly zero) and is called a forward resirtance, whereas it offers a very high resisterce (not exactly infinite) in reverse blased andertion. This high resistance is known as revene revisitent Static & D.C Forward Revistance1-In F.B., the opportion offered by the diode to the direct Current flow is known as Static of D.C. forward resistance The ratio of D.C voltage acron the diode to the D.C current flowing through it gives the value of D. C forward resistance. Static resistance = Forward Dc Current J Centert That is, for any operating point, let the forward Voltage be OA and the Corresponding forward Formand arrent is OB. ... the D.C forward resistance & Static resistance is gluen by  $R_{f} = OA = V$ Fluoto Forward voltage A O

Since the Shape of the diode characteristics is non linear, have the value of RF depends upon the exact location of the operating point on the curve. Dynamic & A.C. Forward Revistorce IF(MA) Dyname c resistance of a PN-Indiade may be defined as the resistance offered by the drode to the A.C. Algored is  $\mathcal{P}$ Called dynamic & A. C. resistance. C Dynamic resistance of a diode B v Cuelty) is equal to the Slope of foroard 0 V-I characteristics of the deode beyond the knee voltage 4 is given by,  $\delta p = \frac{\text{charge in Voltage}}{\text{charge in Current}} = \frac{\Delta V}{\Delta T}$ From the Fig, we observe that charge in forward voltage = AB change in forward Current = CD .. Dyramic of A.C forward resistance (rp) = OB - OA = DV Expression of Dynamic Fondard Resistance we have dide current equation given as,  $I = I_0 \left[ e^{V/nVT} - I \right] - 0$ Differentiating Cq. () win to voltage (V), we get,  $\frac{dT}{dv} = T_0 \left[ e^{v(nv_{\dagger})} \times \left( \frac{1}{nv_{\dagger}} \right) \right]$

$$\begin{aligned} = \int_{T} \int_{T}$$

It is the restricter offered by the PN in drode under Reverse Resistance:sewise beas ardition. Et is very large compared donte forward resistance, which is in due rarge of Soveral Mr. Determine the found resertance of a PN on diade, when the followard Current is 5mA at T=300°K. Asume Problem Forward reststance of a promotiode, Tp = MVT ·Silian.diode Sol1 $r_{f} = \frac{2 \times 300}{11,600 \times 5 \times 10^{-3}}$   $V_{T} = \frac{T}{11,600} = \frac{300}{11,600}$ 2×21 = 52×10-3 5×10-3 = 10.34 -11

24 (22) Transition and Diffusion Capacetorce !-There are basifally two types of Capacetanas aspected with a P-N junction. Space charge of Transition Capaciton (C+);- Depletion Capacit This Corres in to Cur when the P-N m is revere blased. 2) Di ffusion & Storage apacitance (CD)1-This Corres into to cus when the diode is forward blased. (2) depirg in n-Nde Is letter compared Transition Capacitance: Consider a reverse biased PNM. ÐÐ ю ÐÐ Θ the majority Callids move among P ΘĐ €, from the In and the theckness of  $\oplus$   $\oplus$ Θ the depletion layer increases. NOI The width of the depletion layer 12-NASSNO Dis ircreases with in orase in reverse blas voltage. < Wp LLWn = W-Now, the depletion region acts Diston like an insulator & dielectric medium and pard Niregians on esthernide have los resistance and act as the Conducting as Distance Since Capacitor is a dielectric material (insulation) in b/w two Shawn in fig. In-this way, a P-N M may be regarded as a parallel plate capacity.

Scanned by CamScanner

The Sunction apacettence is called the Space charge of transition apacitance. This is denoted by (CT) and is defined  $C_T = \begin{bmatrix} dQ \\ dv \end{bmatrix}$ as where do is the increase in charge resulting from a charge d'u in voltage. Capacitance is nothing but ability to store charge for an applied potential. PN jn is able to store charge in depletion region whech is immobile in voture for a gruen applied potential this we are considering it as a capacitance effect. In general Capacitance C = QBut we are intrested in, For me charge in the potential how much is the charge Stored in the devi a  $C = \frac{\Delta v}{\Delta v}$ So, incremental apacetance of by Cy = da da increase in charge aundby a  $G = \frac{idt}{dv} \left( : i = \frac{da}{dt} \right)$ charge & dv. aurrent is rate of flow of charge per time CT is transition region Capacitance 2 = CT dV Space chaege passier depletion region 11

26 Capacifonce is not a constant, but depends upon the magnitud of the reverse voltage. So CT is defined as, CT = da An Alloy Junction 1\_ & Stepgredidon nype Trivilent PAI BAG Cavider a m in which tree is an abrupt charge from acceptor ions on one side to dond for notice other side. Such a m is formed experimentally. Pos. example; by placing indium, which is trulant, against n-type Ge & heating the Combination to a high temp of of Sare of the indium dissolves into the Ge to charge the Ge from <u>n to ptype at the m</u>. Such a mis Called Alloy & fusto It is not receively the NA = ND it is often advantageous to have an unsymmetrical m. acceptor impusity density is assumed to be much smaller thanks done concentrate NLC much strally than the dones concentration. Net No Smalles Decenso NAT SATD Since Net charge must be Zero, then e NAWP = e Nown In N-side doping Concentration is mole, So width of deplettion in Blide & len is len, En P-Mde in Phide ismole . .... ··· ` Scanned by CamScanner

$$ue frew frot  $C_{T} = \frac{dA}{dv} \longrightarrow 0$

Now let us astate polyadi equation

$$\frac{d^{2}v}{dx^{2}} = \frac{q_{1}N_{A}}{E} \longrightarrow 0$$

where  $E$  is the parent thus by the S. c.

$$\frac{d^{2}v}{dx^{2}} = \frac{q_{1}N_{A}}{E} \longrightarrow 0$$

where  $E$  is the parent thus by the S. c.

$$\frac{d^{2}v}{dx^{2}} = \frac{q_{1}N_{A}}{E} \longrightarrow 0$$

$$\frac{d^{2}v}{dx^{2}} \longrightarrow 0$$

$$\frac{d^{2$$$$

•

2-8 3  $\frac{d\omega}{dv} = \frac{\epsilon}{q_{1}N_{4}\omega} \longrightarrow (5)$ : Q=nqvAL (for Graducte) for n=NA, L=W (oundion width) · Q=NAYAW -> @ defferentiate us.r.to V  $\frac{da}{dv} = N_A v A \cdot \frac{d\omega}{dv} \longrightarrow \textcircled{P}$ · , du = E a Naw = N/A QVA. E QV N/AW  $dq = \frac{\varepsilon A}{\omega}$ But do is the transition Capacitona Cy bend  $C_{T} = \frac{EA}{\omega}$

Scanned by CamScanner

Di-Husion Copartionle (CD):-- when a PN on is F.B., a Capacitance which is much Larger than the transition Capacitarce Comen into picture. This type of Gpacitoria is called the diffusion Gpacifica (CD). C0= -(:: = Ty mean life time  $\begin{array}{ccc} \text{use have} & \text{I} = \underbrace{Q}_{T} \\ \xrightarrow{\gamma} & \begin{array}{c} \end{array} \\ \xrightarrow{\gamma} & \end{array} \\ \xrightarrow{\gamma} & \begin{array}{c} \end{array} \\ \xrightarrow{\gamma} & \end{array} \end{array}$ of darg Cathan) From Diode equation For F.B I = IO e V/NYT -> (2) 0 متر 3 طلای Q=r(Ioeu/nvr) -3 differentiate eq. 3 w.r.t. V, we get do = r. I. d. (ev/n4)  $(:c_{\overline{p}} d_{\overline{q}})$   $(:c_{\overline{p}} = ? I_{c} \cdot e \frac{v(n)^{1}}{n}$ = <u>TI</u> (:: I=Io.e / MA

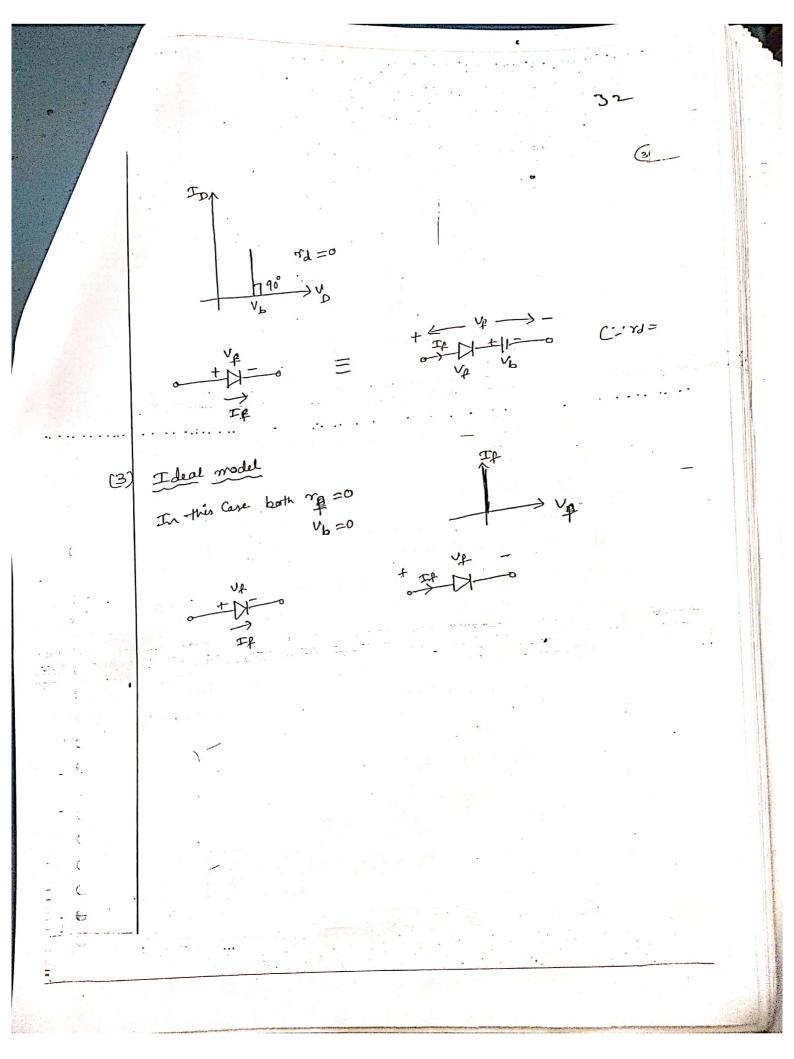

G Diede Equivalent Circuits An Equivalent circuit is a Combination of elements ( like R, L, C etc) properly closen to best represent the actual characteristics of device in a particular operating region. the Canot use circuit analysis techniques like Norton, themerin to fire act parameters like voltage, Current & revistance with the we Can replace actual device with equivalente circulity ... piece where livean courselect cht Grstort voltage drop of Simplified equivalent chits. C1) Ideal equivalent circuit Piece - were Liveas Equivalent circuit (2)ഷ് Anumption After Gradecting it Can be represented interest form -> liveag even with Small non-liveauity glope = tano -> tono = Perpendicular Base Fh slope y = " If Vp slopefort If from ohm's law slope I = rf -) If the V-I Chalackistics is assumed or lines Top = the -Han Forward revisionce is Constart. -> Herce due to this Grapt un canceptale nonlived curve by straightline

- -----

Scanned by CamScanner

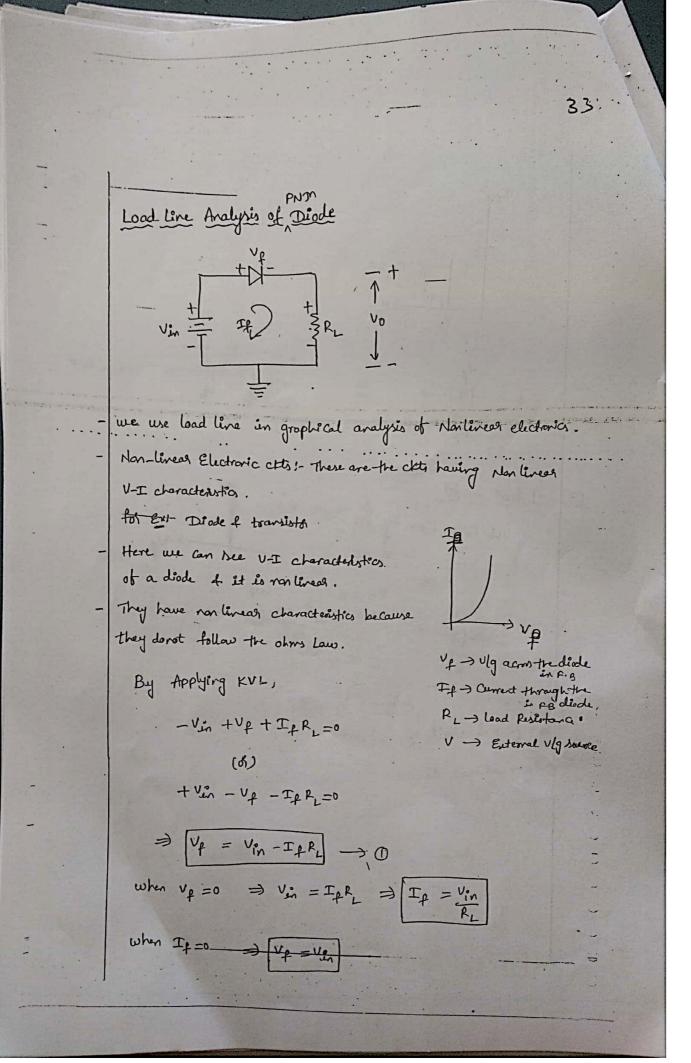

34 h If (mr) Slope of the Load Line Vin = If RL +Vf Vin PL ood live (Vin, o divide B.S by RL Q-pt IpQ  $\frac{V_{in}}{R_{i}} = \frac{T_{f} + v_{f}}{R_{i}}$ VE ya Vin (0,0) Q-pt of Quiliscent pt (G) operating pt = (Ipo) & zunere (O)).  $I_{p} = \frac{-V_{p}}{R_{L}} + \frac{V_{in}}{R_{i}}$ y = mn + c $y = T_{f}$  $C = \frac{V_{in}}{R_L}, m = -\frac{L}{R_L}$ By charging RL, & pt will also charge If  $\uparrow R_L$ , a pt will charge, load live will charge

Scanned by CamScanner

Break dawn Mechanisms in Didet - In reverse biased Gradition as long Brested region VBR as the reverse voltage is laws than break down voltage, the diode current is Small and aborost Constant at Io. Diode Characteristics buyarte Cortain Value; large diode Current flars. This is alled But when never voltage increases breakdown of diode and Corresponding voltage is Called reverse breatdown ustage (VBR) of diode. There are two welterisms due to which the breakdown occur in the diade. These ale (1) Avalanche Break down (2) Zener Break down

Scanned by CamScanner

## Zever Dlode;-

when the reviewse voltage reaches breakdown voltage in growned PNM diede, the Current through the on, and the power diverpated at the on will be high. Such an operation to destructive of the dide gets damaged. whereas diades Can be designed with adequate power dissipation Capabilities to operate in the break down region are Such a dirde is known as zener diede. Zener diede is beauty deped than the ordinaly diate. operation of zeres diade is If (mr) same as that of ordinary PN diode under F.B Graiten. where as under R.B Condition, break our. of the on occuss. - The breakdown voltage dipendy Ip(HA) upon the amount of doping. If the diode is heavily doped, depletion layer will be thin f Consequently, break down occurs at lower reverse without and furtres, the breakdown is tage is sharp. whereas a lightly deped diode has a higher breakdown voltage. - Thus breakdown voltage Can be Selected with the answert of depirg.

### Scanned by CamScanner

Scanned with CamScanne

36

31 Zener Breakdour Avalanche Breakdown 1. Breaking of Covalant bands is due to interse electric field across 1. Breating of Gratent bards is the narrow depletion region. This due to Collision of accelerated Jereroles Large ro. of free electron aherge Carrier having large velocities and kinetic energy with to Guve breakdown. adjacent atoms. The procen is alled 2. This occurs for zerar diodes arrier multiplication. This occurs of zeror dide ... with VBR lass often GV. with VBR greater year GV. 3. The temperature Coefficient 3. The temperature Coefficient is regative. is positive. 4. The breakdown voltage decreases 4. The breakdown voltage increases as junction temperature increases as the junction temperature increases . 5. occurs for heavily doped diode The occurs for lightly doped 5. diody. B, The V-I characteristics is very G. The V-I characteristics to rut as Bharp in breatidown regime. Storp as Zever breakdown in breakdown region. JBP2 I. JBR Notion Sharp as Zeres z. Lineon Graded Junction Step groded sunction 7.

Appli Cations in

Suprbol

Wirnd - Thom

from the Zever characteristics, under the R.B. Ordition, The Voltage across the diode remains almost astrongh the Current through the diode inscreases. Thus, the voltage across the Zeverdiode Serves as a reference voltage. Hence, the diode Can be used as a voltage regulation.

33

6.

VE ZRL VO às a vo trage regulates

ener Dide:

Zener dide is a reverse biased heavily-doped Silicon P-N junction diade which is operated in the break-down region. The Symbol of zener diode is shown in fige). This is similar to a normal diode except the line representing the cathode is bent at both ends i.e. Anode Casthoole (A) + - - (1) like the latter z for zener. fig(): Symbol of Zenel diode V-I characteristics: The V-I characteristics of zener diade under betward bias and Reverse bias is shown in fig:c). When a zener is Found loiased its chalacteristics are just as those of ordinary diccle. The fig() shows that when zenel reverse applied voltage its increased, at Vz cutrent increases greatly. In Vz F2 (min) This voltage is called as L Zener bleakdown Avalante / zener voltage (v2) (21) breakdour breakdour Jz(max) Voltage. Sigil) V-I chalacteristics 7 zener diode.

#### Scanned by CamScanner

39

There are two mechanism of the breakdown. Breakdown Mechanism"

Zener breakdown takes place in very thin junction (i) Zener breakdown s when both sides of junctions are heavily doped then the depletion layer becomes nations. When a small reven bias voltage is applied, a very strong electric field is set up across the thin depletion layer. This field is enough to break the covalent bounds. Now very large number of elections and holes are produced, which Constitute the Severse current (zener coursent). (ii) Avalanche breakdown & Joped and the depletion larger jus - If applied severse brase increases, the field acrossitle jn increases. Theemally generated carlielle (minacity) aquire a large amount of energy from the this field and starts distrupt Covalent bond by colliding with immobile ions and Creater new electron-hale pails. These new Carriels again acquire sufficient energy from the field and Collide with other immabile cont and generating further election-hole-pain. This process is cumulative in nature and results in generation of avalanche Glood, of charge carriers within a shart time.

Scanned by CamScanner

valenche maltiplication.

Application of zenes dicde;

-> Used as a voltage segulator. -> Used as peak clipper

Tunnel Diode:

Trannel diode, is a Extremely heavily doped, This junction diode. Also called Esaki diode.

An ordinary de PH junction diode is doped by imparity atoms in the concentration 1 part in 108. with this amount of doping, the width of depletion layer is wide and exists a potential barrier acress the junction Due to this potential barrier majarity change carriers carit closs the junction.

If the concentration of impurity atoms is gleatly indeased in a PN Junction i.e., 1 part in 103, the device characteristics are completely changed. Under this condition, a very this depletion layer forms, and the consider close the junction even if they do not have enough energy to overcome the potential barrecelars & 0.7-si). This is known as tunneling phenomenon Symbol:

#### Scanned by CamScanner

V-I characteristict of Tunnel diode can be V-I chasacteristict: explained well using Energy band structure of a heavily doped PN diode. Breigy band diagram 4 V-I chara ateristics are as shown in fig: ( ), () respectively. C·B Barrier Ep Turneling Holes VB . (a) when small forward biased (6) Full tunnelling EF EF EC Ev -777\_EC EF (d) After Valley Vo Hage (C) After Peak Voltage

> Consider now that a forward bias is applied to the diode, so that the potential harrier is decreased below Eo. Hence the noside levels must be shift upward with respect to those on the p-side, and the energy-band picture for this situation is indicated in big: ()a. It shows that energy levels of elections occupied in The conduction leand of the nonoterial (the heavily shaded level) are same as allowed empty states (holes) in the valance band of the P-side. Hence electrons will tunnel from the n-to the P-material, giving rise to the followed cullent, of shown in V-I chain fig() -> At the forward bias is increased further, the Condition Shown ing fig () b. it leached. Now maximum number of electrons can leave right side of the Jry and tunnel through the barrier to the left side, giving like to the peak current Ip in fig1), another Voltage is peak voltage Vp. > If still mole folward bias is applied, the Situation in fig()c. is obtained and the tunnelling current decreaser. Finally, at even large barnaed biat, fig() d. is obtained, there are no equal energy levels in both side, so turnelling stops. The paint is- known as valley point (4, Ir), After this point It torward bias increased, it acts acts as a ordine

44 (42) Valt - Ampele characteristics of Tannel dide A\*1. Vp-> Peak voltag Ferrisol Vy -> Valley volto Ip→ Peak Curren Tr Iv -> Valley Curser Ti -> Forward vottage Np Negative Resistance fevere vollet Region 1 pevere Eccellent Current conduction (Revence) Also Doon as the F.B is applied significant current is produc The Current quickly reaches its peak value Ip. when forward Vottage reactors a value Up. It is denoted by point A. 2 when folward voltage is further increased (i.e., > Vp), the current starts decreasing to I'v corresponding to valley Voltage (Vu). This is denoted by point B. Thus from Point A to B, the current decreases as voltage increases, this results in a regative resistance. -> The position AB Constitutes the most useful property of the diode. That is instead of obsorbing power, a the resistance produc -> poures.

-> For voltage greater -than Vy arment starts increasing as in case of a convertional diode. AppliCation of Tunnel diode)-(1) ultra high speed switching davia High frequency oscillate (microwave oscillator) (2) Digetal design 3) Comparision of zeres and tunnel doody Tunnel Zever Feature g emenden of Made up. f Construction Made up of 31 with gallum asseride with two time layers (P-N) Layers (P-N), galliumarsenste is preparad Heavily doped Heavily doped Doping Echebets regative resisting Acting as breakdown operation device at reverse bias at F.B Constant voltage Sara Microwave oscellato Applications ultra high Speed Switching Voltage regulator devi a

45

## Varactor diade!-

\*

It is also termed as voltage <u>variable Capacitance</u> die de, of Vari Cap,

we know that the depletion region in a P-N In terms a barnier which seperates the iter of the grave charges on each side of the JN and the depletion region acting like a dielectric. Thus a PN IN possesses Junction Capacitance. When a reverse bias is applied, the function Capacitance decreases because the depletion region width increases.  $\boxed{\cdots}C_T = \underbrace{E_I}_{cc}$ A variator diade is specially menufactured P-N Junction with suitable impunity Carantration and operated under R.B Conditions so as to yield a variable Junction Capacitance.

Symbol

working !-The circuit of R.B varacte diade is shown in fig dielec when R.B voltage is increased, the depletion Louger becomes widered. This increases the dielectric thickness. As a result the apacitance is reduced. on the other hard, when revenue beas voltage is decreared\_ the depletion layer becomes narrowers. This decreases the dielectric thickness. In this case the Capacitance is increased.

Equivalent circuit

### Scanned by CamScanner

4-6

(1-1

Scanned with CamScanne

-

Fig. Shows the variation of diode piode apacitane Capacitance as a function of applied R.B. Voltage. From the fig. the variation of Gapacitance is manimum when ō R. B voltage is zero q it reduces Peverse Vottage non-linearly as the R.B collage increases. hig:- Revene voltage verses diode Capacita Types of Varactor diodel-There are two types of varactor diode profile! (11, Hyper about profile (i) Abrupt doping profile Non uni tom doping uniform depin

In abrieft depirg profile, the deping is uniform on both Sides of the junction and the tuning range of Capacitance is 4:!!

→ In Hyper aboupt profile, the doping level increases towards the junction as shown in fig. [1]. In this Case due to mallades depution layer, a large Capacitance occurs at the junction. BO, a small charge in reverse bias voltage makes a larger, Variation in Capacitance. Due to thes creases, turing range is 10:1.

Scanned by CamScanner

Scanned with CamScanne

47

48 64 Applications --1. varactér d'ode is used in automotic frequency Control. It is used in turing circuits. 2. 3. used in adjustable bard pass filter. 4 SCR (Silian Grandled Rectifier.) Arderph 51 N J2 P J. (حملع) N -> It is a four layer servi Cordiacte device being alternate of P-type & N-type Silian. It Consists of 3 junctions J1, J2, J3 & Sterminals Arode (A), Catrode (K) & Gate (G). SCR is a unidirectional device. (J, ZT3 operates in F.B & Operation : -The operation of SCR Can be totadied (i) when the gate is open (ii) when the gate is five worto Etredes

сb when the gate is open, It is shown in the big, no voltage is Р applied at the gate. from the fig. 5, N Ji & J3 ale F.B while the Junction P σ, J2 is R.B. Due to R.B J2, rowred N flaus-through RL and hence BCK is Cut -off. However when the arode (F.B) Wittage is increased a certain critical value (Broatcour voltage) is reached then the Junction J2 breaks down. SCR now Starts Conducting heavily and is said to be in ON state. when the gate is positive wirito Cathedes. ຕ່ຳ As shown in fig: J3 is F.B, so at Very small Gate voltage Gate current M P Sturits flaving, Due to the Gale 53 N aurrent, avode aurrent increases. In an cutremely Dwall-time, Jundian J2 breaksdain & BCR Conducts heavery. ance SCR storts Conducting, the gate loves all controls. That is to turn OFF BCK, Bupply Voltage is reduced to Zelo.

50 (43) Points to remember 1-If the anode is made i we warto Cothode file, J. E.J. R.B. SCR is blocked & no current flows, If " Jue vollage increases breakdown occurs & SCR is destroyed. It shows that SCR is unidirectional device. Is see an tum on either by keeping the gate open & making The supply voltage equal to breakous voltage of by applying Small voltage (type Cally 1.50) to the gate & making the Supply voltage hers than breakous voltage. -> Either SCR does not Conduct of conducts heavily. This SCR behaves leke a surtch. to turn off SCR, supply voltage is reduced to zero. V-I characteristics of SCRI-ON Jole (IG V-I characteristics of SCR for IG=0 (i.e gape is open) is shown in fig. TH Forward Characteristics:-DI L Break when the anode is "the wor to Cathode, the chalacteristics is known as friended TR characteristics. It is shown in fig! by OABC Curve,

when the bupply voltage is increased from zero, a point A is reached then SCR Starts Conducting. The voltage at point A is called as forward breakover voltage At this voltage Junction J2 breats down & SCR Quintches Suddenly to high Corducting state. Break over vottage is defined as the minimum forward ustroop at which SCR Starts Grauching heavily. At this movement, the voltage acron SCR building drops as shain by dotted curve AB. At Point B Current is Called as holding Current IH. The holding Current is the maximum arede Current at which SCR is turned off from ON Gradition. \* There is a manimum value of arede Current which an SCR is Capable of pawing without destruction. This is known as followed current rating and is expressed by IF ( about 30.A to 100 A). - Reverse biased characteristics--) when anode is "Jue wirito Cathode, The characteristics is Called as reverse characteristics. when the avoid woltage is gradually increased, at first the arode current remains small (i.e., heakage current)

## UNIT-II

## Rectifiers and Filters

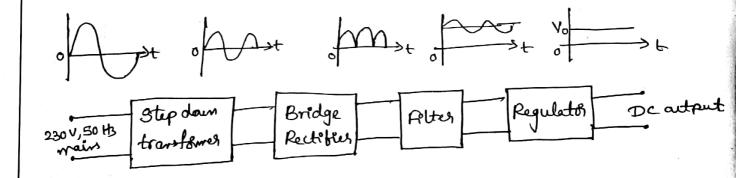

INTRODUCTION: All electronic circuits need dc power supply either from battery & power pack write. It may not be economical f Conversient to depend upon bottery pawer supply. Hence, many electronic equipment Contain circuits which Convert the ac hupply voltage into dc Noltage at the required level. 1. Linear mode power supply (LMPS): - ac to dc 2. Switched mode Power Myply (SMPS): - dc to dc, dc to ac - Turks ac (230V, 50 Hz)

Ψ

## Rectifica:-

Rectifier is defined as an electronic device used for Converting ac voltage into unidirectional voltage. - A Rectifier utilizes unidirectional Conduction device like a Vacuum diode & PN junction diode. - Rectifiers are classified depending upon the period of Goduction as Half-wave rectifier and full-wave rectifier.

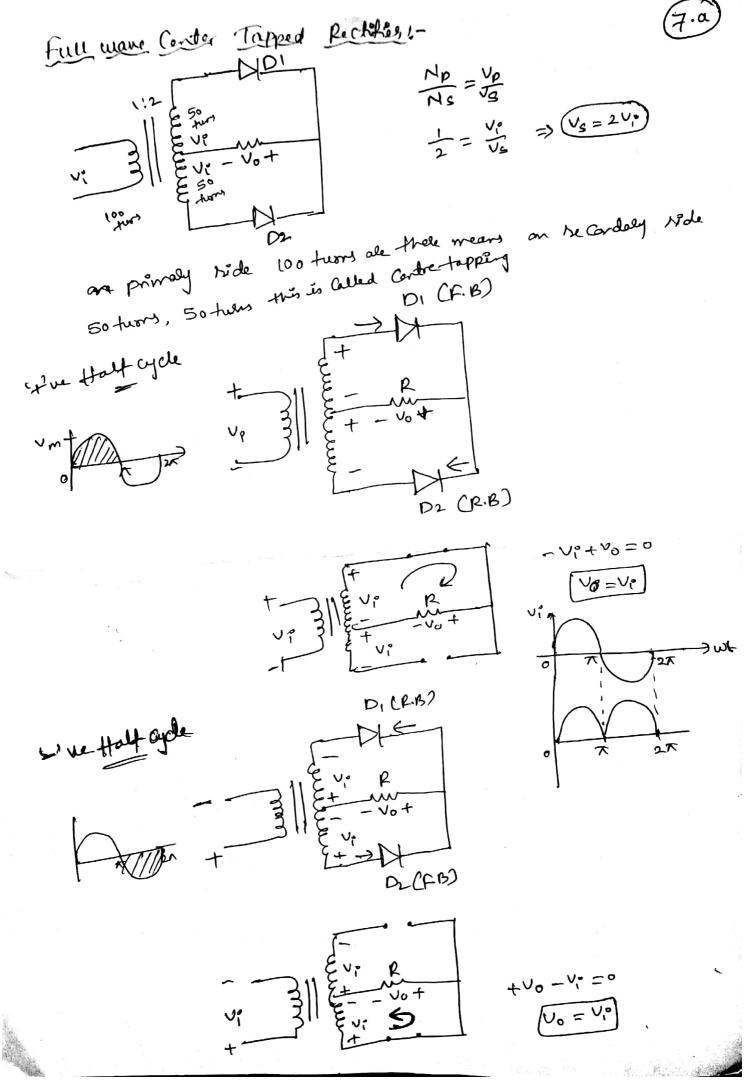

Rectifier Circuit Half - wave Peck fies full mane fect fleg - uses only are di ade Bridge FUR - Hardly used in practice Canton top FUR Centre tap - Needs no transformed - Needs a Centre tap uses four di odes transformed - Mostly used in - uses two diodes practic

Centre tap transformed is expursive, so we are going for Bridge FWR.

# UNIT-II Rectifiers and Filters

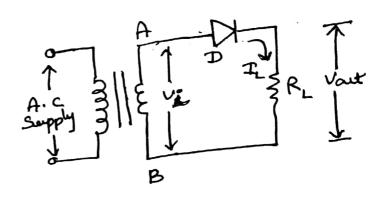

The P-N junction diode as rectifier. In diode readily Conducts under F.B F.B -> diode Conducts R.B -> diode does not Graduct If an atternating vig is applied across the diode terminals, diode is F.B -> during 'the half-Cycles P.B -> 'Live half-Cycles

Hence if a Single diode is used for rectification, Conduction occurs only during "the half-cycles. This is <u>half-wave rectification</u> If we are using two of four diodes, Conduction occurs during both positive of negative half-cycles. This is full-wave rectification

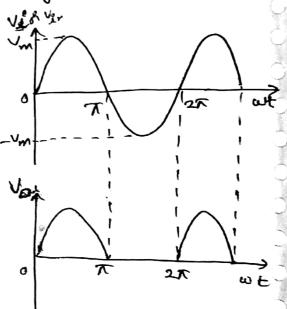

Half-wave rectification,

A diade D and Load resists RL are Convected in Series, and the alternating Voltage to be rectified is applied directly across the Series Combinetian, if no transformed used.

However, if a transformer is used, let it be assumed that end A of the Secondary winding is 'the during a positive half-cycle of V3, The diode D is F.B & bence it Conducts.

A Current flows through the load resistor RL.

- During the '- we halt cycle of Vs, and A becomes negative. (and B would be positive than) and the diode gets reverse brasely. It does not conduct and hance there is no subject current through Br.

- The diade Conducts again during the Subsequent 't've half Cycle and there is flow of current through RL.

elpvlg are Suppressed.

- The rectified ofp. i.e., Current IL is unidirectional, but it is not pure d.c., nor is it Continuous. It is termed as pulsating d.c.

$$V_{t} = V_{m} \sin \omega t$$

$$V_{n} \rightarrow Peak value$$

$$V_{0} = \int_{0}^{V_{m}} \sin \omega t \quad fh \quad 0 \leq \omega t \leq \pi t$$

$$0 \quad fh \quad \pi \leq \omega t \leq 2\pi t$$

$$\omega hese \quad V_{m} = T_{m}R_{L}$$

$$dc \quad voltage \notin currect:-$$

$$V_{0}v_{g}(\theta) \quad V_{dc} = \frac{Area \quad urder tre \quad curve}{base}$$

$$= \frac{2\pi}{2\pi} \int_{0}^{\infty} v_{0} \quad d(\omega t)$$

$$= \frac{1}{2\pi} \int_{0}^{\pi} v_{0} \quad d(\omega t)$$

$$= \frac{1}{2\pi} \int_{0}^{\pi} v_{0} \quad d(\omega t)$$

$$= \frac{1}{2\pi} \int_{0}^{\pi} v_{0} \quad d(\omega t)$$

$$= \frac{V_{m}}{2\pi} \left[ G_{0} \omega t \right]_{0}^{\pi}$$

$$= \frac{V_{m}}{2\pi} \left[ G_{0} \omega t \right]_{0}^{\pi}$$

$$= \frac{V_{m}}{2\pi} \left[ (t+i) = V_{m} \right]_{0}$$

$$i \quad \int_{0}^{\pi} V_{dc} = \frac{V_{m}}{\pi}$$

$$i \quad \int_{0}^{\pi} V_{dc} = \frac{V_{m}}{\pi}$$

$$I_{dc} = \frac{V_{dc}}{\pi}$$

$$= \frac{V_{m}R_{L}}{\pi R_{L}} = \frac{T_{m}R_{L}}{\pi R_{L}} \quad (i + i) = T_{m}R_{L}$$

-

5

5)

S

Scanned by CamScanner

199

\*

(2) Times value of old voltage 5 curvet:

$$V_{mm,s} = \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} V_{0}^{h} dwt$$

$= \sqrt{\frac{1}{2\pi}} \int_{0}^{2\pi} V_{m}^{h} 2iihwt dwt$

$= \sqrt{\frac{1}{2\pi}} \int_{0}^{2\pi} V_{m}^{h} 2iihwt dwt$

$= \sqrt{\frac{1}{2\pi}} \int_{0}^{2\pi} (\frac{1-(0+2wt)}{2}) dwt$

$= \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} (\frac{1-(0+2wt)}{2}) dwt$

$= \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} (\frac{1-(0+2wt)}{2}) \int_{0}^{\pi} (\frac{1}{2}) \int_{0}^{2\pi} (\frac{1}{2}) \int_{0}^{2\pi}$

24-24

$\bigcirc$ (4) 5 (3) Rectifier efficiency !-0) The Rectifier efficiency is defined as the ratio of d.c. autput power to the a.c input power. M = d. C. Power delivered to the load a.c. input power from transforma  $= \frac{P_{dc}}{P_{ac}} = \frac{V_{dc} \ I_{dc}}{V_{rms} \ I_{rms}}$ = Vdc  $\cdot \frac{Vds}{RC}$ Voms, Voms  $= \frac{V_{dc}^{2}}{V_{mm,s}^{2}} = \frac{V_{m}^{2}/\pi^{2}}{V_{m}^{2}/2^{2}} = \frac{4}{\pi^{2}} = 0.406$ = 40.61, (1) Ripple factor (V) :- The ratio of ome value of a Component to the dc Comparent in the autput is known as repple factor. V = - Toms value of ac Groponent dc value of Groponent No = Vac Vr - mpple vottog (Vac)mi Vde D = (Vojems). Vd c ac Inpple whole (Vr) mms = VV2mms-Vdc V = (Vm) - 4

$\mathbf{o}$

0

5

5

3

3

3

6

Э

Ô

0

$\mathcal{O}$

G

D

Ĉ

D

$\bigcirc$

(This means that if the transformed rating is [KVA(1000VM) ) balf mare rectifier Can deliver 1000×0.287 = 287 malts ) to load resistance. Peak Inverse voltage (PIV):-It is defined as the maximum Voltage across the without destroying the junction diode in the reverse direction, i.e., Vm. Peak of a regative ballow (F) Peak of a regative II Vm Form Factor (F): - The Form factor F is defined as  $F = \frac{3}{2} \frac{3}{2} \frac{1.57}{1.57}$ (8) Peak factor :- at is defined as the ratio of peak value to rims value (9) :, Peak factor =  $\frac{\text{Peak value}}{\text{rms value}} = \frac{\text{Vm}}{\text{Vm}/2} = 2$ Problemsh (1) A halt-mare rectifier, having a resistive load of 1000-2. rectifiesan alternating voltage of 325V peak value and the diode has a forward revistance of 100-2. Calculate (a) peak, average and oms value of current (b) dc paues autput (c) ac input power (d) efficiency of the rectifier. (a) Peak value of Current, Im =  $\frac{V_m}{rp+R_L} = \frac{325}{100+1000} = 295.45$

Auroge Currents,

$$I_{dc} = \frac{T_{m}}{R} = \frac{295.45}{3.14} = 94.046 \text{ mA}$$

is

RMS value of Current,  $T_{mrs} = \frac{T_{m}}{2} = \frac{295.45}{2} = 147.725 \frac{1}{ma} t$

(b) DC powers actput,  $P_{dc} = I_{dc}^{2} \times R_{L}$

$= (94.046) \times 10^{-3})^{2} \times 1000$

$= 8.845 \text{ W}$

(c) AC input power,  $P_{ac} = (I_{mrs})^{2} \times (r_{f} + R_{L})$

$= (142.725 \times 10^{3})^{2} \times (1000) = 24 \text{ W}$

(d) Efficiency of rectification,  $T = \frac{P_{dc}}{P_{ac}} = \frac{8.845}{24} = 36.85\%$

(e) A HUR has a load of  $3.5 \text{ K.S.}$  If the diode resistance

and Secondary Gel resistance together have a resistance

of Peak value 240V. Gl culate

(i) Peak, auroge and the input voltage has a Signal voltage

of Peak value 240V. Gl culate

(j) Peak, auroge and the rectifier.

Selin load resistance in a HWR,  $R_{L} = 3.5 \text{ K-L}$

Diode and Secondary Gil resistance ,  $r_{F} + r_{S} = 800.2$

Peak value of input wittage = 240V

7

(1) Reak value of Current,

$$T_{mn} = \frac{V_{mn}}{Y_{n}+Y_{p}+R_{L}} = \frac{240}{4300} = 55.81 \text{ mm}$$

Average value of Current,  $T_{dec} = \frac{T_{m}}{T} = \frac{55.81 \times 10^{-3}}{T} = 17.77 \text{ mm}$

RMS value of Current,  $T_{rms} = \frac{T_{m}}{2} = \frac{55.81 \times 10^{-3}}{2} = 27.905 \text{ mm}$

(1) Dc power adopted is

$P_{dc} = (T_{dc})^{2} R_{L} = (17.77 \times 10^{3})^{2} \times 3500 = 1.105 \text{ cm}$

(1) Ac power input is

$P_{ac} = (T_{rms})^{2} \times (596 R = (8.4)^{-3})^{2} \times 4300 = 3.34 \text{ mm}$

$= (0.16)^{1/2} \times 896 R = 18.94$

(2) Efficiency of the readerfrees is

$T = \frac{P_{dc}}{P_{ac}} = \frac{1.105}{3.348} \times 100 = 23\%$

(3) A half-word readerfrees is used to hupply 24.4 dc to a

resistive load of 500-L of the object has a followed resistance

of 50 L. Calculate the maximum value of the ac voltage

required at the input.

Average value of load current,  $T_{mc} = \frac{7V_{dc}}{R_{L}} = \frac{24}{500} = 48 \text{ mm}$

Hantonium value of load current,  $T_{m} = \pi \times T_{dc} = \pi \times 48 \text{ mm}$

$Hantonium ac voltage required at the input,

$V_{m} = T_{m} \times (T_{p} + R_{L})$

$= 150.8 \times 10^{-3} \times 550$

$= 82.94 \text{ M}$$

de

An ac supply of 230V is applied to a half-view rectifier (4) circuit through transformes of turns ratio 5:1. Ansume the diode is an ideal are. The load resistance is 300 m, Find (a) de autput voltage (b) PIV (c) maximum and (d) average values of Power delivered to the bad. Ard - (a) The transformer Secondary voltage = 230 = 46 V Boted voltage of the transformer Secondary is the Manimum value of Secondary Voltage, Vm=V2x46=65V i de olp voltage, Vac = Vm = 65 = 2017V PIV of a diode = Vm = 650 (ይ) Manimum Value of Load Current, Im= Vm = 63 RL 300 (2) = 0.2174 . man value of Power delivered to the load,  $P_{m} = T_{m}^{2} \times R_{L} = (0.217)^{2} \times 300 = 14.100$ (d) The average value of lood current,  $I_{dc} = \frac{V_{dc}}{R_L} = \frac{20.7}{300}$ = 0.069 A i. any value of Power delivered to the load  $\rightarrow P_{ac} = I_{dc}^{2} \times R_{L} = (0.069)^{2} \times 300 = 1.43 \omega.$

Ð Full wave Rectifier :-Jim AC VON ALL VIII CONTRACTOR pr we Jm. J, 2 Not Jm for end- workers spus It Converts an ac voltage into a pulsating dc voltage using both half cycles of the applied ac voltage. It uses true déodes of which are conduct, during are half-Cycle while the other diode conducts dueing the other half-cycle of the applied ac voltage. Fiß During positive half cycle => D, be Groves possitive of D2 be Groves regative P2 be Groves regative D, Conduct D2 abres not Grouce The load current flows through D; and the voltage drop across R, will be equal to the input voltage. Derry regative half cycle of the inpelt => D, be Gresregative D, does not and ucr The load Current flows through D2 and the voltage drop above R1 well be equal to the input voltage.

0

$\bigcirc$

0

)

$\bigcirc$

)

(1)

$$V_{0} = \int_{1}^{V_{0}} V_{0} \sin \omega t \quad 0 \le \omega \le \le \pi$$

where  $V_{0} = T_{0} R_{L}$

(1)  $dc$  Voltage  $\xi$  carried

$V_{ung}(A) V_{dc} = \frac{\beta earned}{period of the cycle}$

$= \frac{1}{\sqrt{5}} \int_{0}^{V_{0}} d(\omega t)$

$= \frac{1}{\sqrt{5}} \int_{0}^{T} V_{0} d(\omega t)$

$= \frac{1}{\sqrt{5}} \int_{0}^{T} V_{0} d(\omega t)$

$= \frac{V_{m}}{\sqrt{5}} \left[ -C_{0} \omega t \right]_{0}^{T} = \frac{V_{m}}{\sqrt{5}} \left[ -C_{0} \kappa + C_{0} 0 \right]$

$= \frac{V_{m}}{\sqrt{5}} \left[ -C_{0} \omega t \right]_{0}^{T} = \frac{V_{m}}{\sqrt{5}} \left[ -C_{0} \kappa + C_{0} 0 \right]$

$= \frac{V_{m}}{\sqrt{5}} \left[ -C_{0} \omega t \right]_{0}^{T} = \frac{V_{m}}{\sqrt{5}} \left[ -C_{0} - C_{0} + 1 \right]_{0}^{T} = \frac{9 V_{m}}{\sqrt{5}}$

$I dc = \frac{V_{dc}}{R_{L}} = \frac{2 V_{m}}{\sqrt{7}R_{L}} = \frac{2 T_{m} \beta L}{\sqrt{7}R_{L}}$

$I dc = \frac{2 V_{m}}{\sqrt{5}} \left[ \frac{1}{\sqrt{5}} \sqrt{\frac{5}{6}} d(\omega t) \right]$

$= \sqrt{\frac{1}{\sqrt{5}}} \int_{0}^{T} \frac{1 - C_{0} 2\omega t}{\sqrt{5}} d(\omega t)$

$= \sqrt{\frac{1}{\sqrt{5}}} \int_{0}^{T} \left( \frac{1 - C_{0} 2\omega t}{2} \right) d\omega t$

$$= \sqrt{\frac{V_{m}}{2\pi}} \left[ (\omega t)_{0}^{R} - (\frac{g_{in} 2\omega t}{2})_{0}^{R} \right]$$

$$= \sqrt{\frac{V_{m}}{2\pi}} \left[ (R-0) + (\frac{g_{in} 2R}{2} - \frac{g_{in} 2(0)}{2}) \right]$$

$$= \sqrt{\frac{V_{m}}{2R}} \left[ (R-0) - 0 \right]$$

(3) Rectifies efficiency:

$$\begin{aligned}

\mathcal{N} &= \frac{P_{dc}}{P_{ac}} = \frac{V_{dc} \cdot E_{dc}}{V_{ms} \cdot E_{mn}} = \frac{V_{dc} \cdot \frac{V_{dc}}{R_{L}}}{V_{ms} \cdot E_{mn}} \\

&= \frac{V_{dc}}{R_{L}} \cdot \frac{P_{L}}{V_{ms}} = \frac{V_{dc}^{2} \cdot \frac{V_{dc}}{R_{L}}}{V_{ms}^{2}} = \frac{2V_{ms}}{R_{L}}^{2} \\

&= \frac{V_{dc}}{R_{L}} \cdot \frac{P_{L}}{V_{ms}} = \frac{V_{dc}^{2} \cdot \frac{V_{dc}}{R_{L}}}{V_{ms}^{2}} = \frac{(2V_{m})^{2}}{(2V_{m})^{2}} \\

&= \frac{4V_{m}}{R_{L}} \times \frac{2}{V_{m}} = \frac{8}{R^{2}} = 0.812 \\

&= \frac{9}{R_{L}} \cdot \frac{1}{R_{L}} \cdot \frac{1}{R_{L}} = \frac{1}{R_{L}} \cdot \frac{1}{R_{L}} \cdot \frac{1}{R_{L}} \\

&= \frac{1}{R_{L}} \cdot \frac{1}{R_{L}} \cdot \frac{1}{R_{L}} \cdot \frac{1}{R_{L}} = \frac{1}{R_{L}} \cdot \frac{1}{R$$

Ripple Factor:- $V = \frac{(V_r)_{rms}}{V_{dr}}$ (Vr)rms = JVms - VLc  $v = \sqrt{\left(\frac{v_{max}}{v_{AC}}\right)^2 - 1}$  $= \int \left( \frac{V_{y}}{1\sqrt{2}} + \frac{\pi^{2}}{4} \right) - 1$  $= \int \frac{\pi^2}{8} - 1 = 0.48^2$ V = 0.482 For F.W.R

(4)

(5) Regulation:

Load regulation Y =

$$\frac{V_{NL} - V_{FL}}{V_{FL}} \times 1007$$

.

live regulation Y =  $\frac{V_{FL} - V_{NL}}{V_{NL}} \times 1007$ .

Transformer utilisation factor TUF = <u>Pd.c</u> = <u>Vdc Idc</u> <u>other</u> Pa.c(roted) = <u>Vac(roted)</u>. Iac(roted) **(6)**  $= 2 \frac{1}{2} \frac{1}{1} \frac{1}{1}$  $\frac{\sqrt{m}}{\sqrt{2}} \cdot \frac{1}{\sqrt{2}} = \frac{8}{\pi^2} = \frac{0.812}{\pi^2}$

$$\frac{1}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{2 \times 70 F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f} \frac{1}{printing} = \frac{10 \cdot 5F \circ f}{10F \circ f}$$

Ì

্ ৩

Ų

)

Transformer transform (changes) Light ulg to be outge of

Step down transformers (Voltrage has been stepped -down)

5:1

220N 311 a AeV

$$r_1 = m_1 - 3$$

step due

$r_1 = m_1 - 3$  step due

$r_2 = m_1 - 3$  step due

$r_1 = m_1 - 3$  step due

$r_2 = m_1 - 3$  step due

$r_2 = m_1 - 3$  step due

$r_1 = m_1 - 3$  step due

$r_2 = m_1$

| A contraction                                                      |                    |           |                  | (b)                |

|--------------------------------------------------------------------|--------------------|-----------|------------------|--------------------|

| dis adu af Pruz I - unage "Fander Happed the<br>Gatur, bulker 2 um | Compalision of Red | Holf-wave | full-wave        | Bridge             |

|                                                                    | No.of diodes       | F         | 2                | 4                  |

|                                                                    | n (efficiency)     | A0.6%     | 81.2%            | <u>क्वा - २7</u> . |

|                                                                    | Vd c               | Vm/T      | 2 m/ T           | 2Vm/r              |

|                                                                    | Voms               | Vm/2      | vmlsz            | Um /52             |

|                                                                    | f:pplefacts(V)     | 1,21      | 0.48             | 0.48               |

|                                                                    | PIV                | Vm        | 2 <sup>V</sup> m | Vm                 |

|                                                                    | Form Factor        | 1.57      | 1.11             | l.j.i              |

|                                                                    | Peak Factor        | 2         | 52               | 52                 |

|                                                                    | TUF                | 0,287     | 0,46             | 0,81               |

Advartages of Halt wave Rectifies :-- Simple Circuit - Low Grt Disaduantages of Haltwave Rectifier, - Low rectifier efficiency - Higher ripple factor Low TUF Advantages of full wave Rectifreg: - Equal currents flow through the two halves of the Cardre topped GeCondaly of the paws transformer in opposite directions. Hence de saturation of the Core is avoided. - Higher ripple frequency of Lower ripple factor permits use of cheaper Smoothing filter. - Higher olp voltage, higher olp power of higher TUF. - Higher redifier efficiency. Drow backs of Full wave Rectifies1-- More circuit clements - Higher Cost. - annerts in both the Primary fitre Secondary of the powers toansformer flow to the entire a.c. Cycle & hence to a given pover autput, pover parother of a small Size may be used in Comparision with that in a full wave bectifies. - No Contretap is needed in the transformer, secondary. - Since two diodes all plesent in hiries in each Conduction path, pIV-rating of each diode is only Um. Hence bridge Kecht Aug is highly Suited for High Voltage application. Disadurateges of Bridge Rechificol Four diodes all needed - load resists of the sauce have no common point which may be earthed. - During each falf ajole, two diodes are present in Series in Each Orduction path, PIUrading of each diode is only Um. thra bridge Receipting is highly sustained for

Scanned by CamScanner

for Half of de D1 (F.B) + DA (R.B.) f ve that eyde ON ON DI D3 DI D3 D3 - we that ayou in ve Halt ayche 0 R.B na 0104 FB. 0 1-total of P Vo くう Vac Operation 1-During the five half cycle, terminal Miss & re while the femiral N is -'ve. In this situation diedes Dy & D3 → F·B, aduer Ferninal N D2 3D4 -> R.B, downot Conduct- Current flass along MABEFN. There is a vig drop a cron R. During the sue half lych, terminal M is sive, N is sive, D2 & DA -> F.B, Conducts, D1 & D3 -> R.B -> dores not a duct. Now Current flows along MAEBEN. The current produces a vly drop acron Rc. the Eument through the RL is in have direction in both half cycles. Analysis. '. - $V_{dc} = 2 V_{m}$ ,  $T_{dc} = 2 T_{m}$ ,  $V_{r,m,s} = V_{r}$ ,  $T_{r,m,s} = T_{m}$ N=0.812 Cd) 81.27., V=0.48  $TUF = (TUF)_p + (TUF)_s = 0.812 + 0.812$ 20.812 piv: - It is um for each deode

Scanned by CamScanner

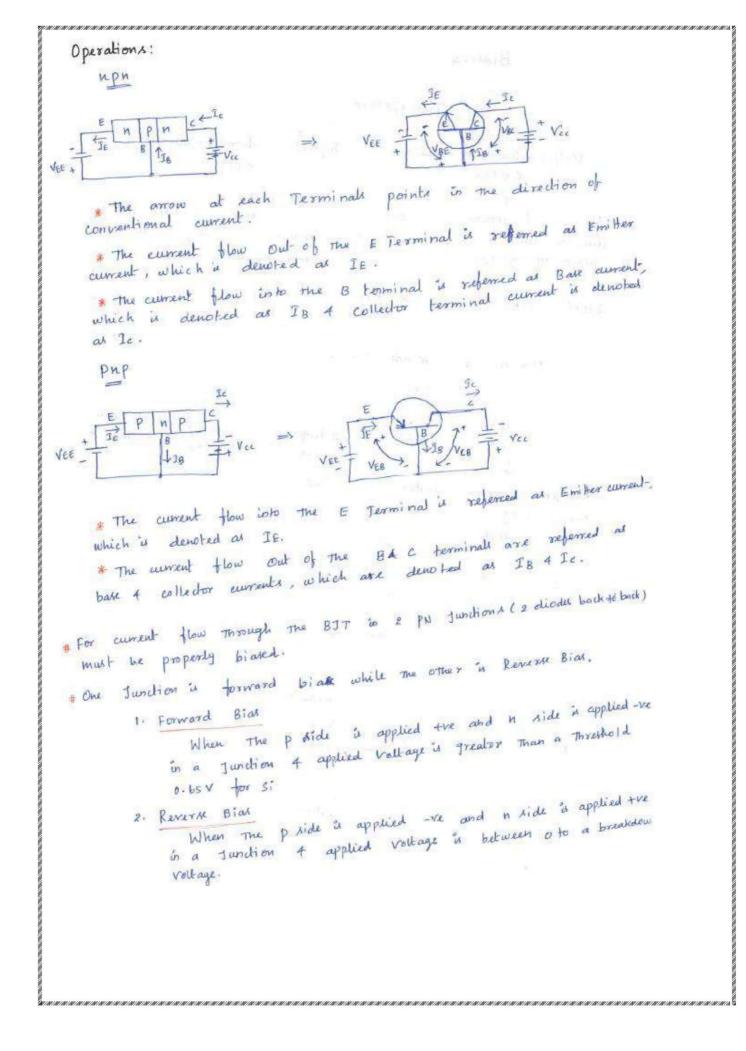

## UNIT- III TRANSISTOR CHARACTERISTICS

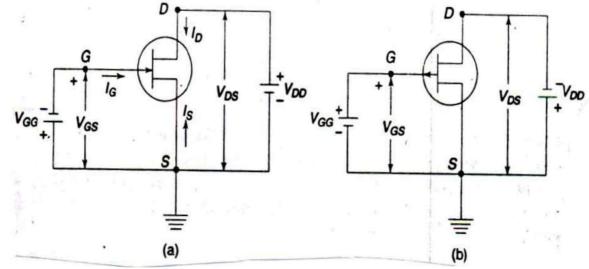

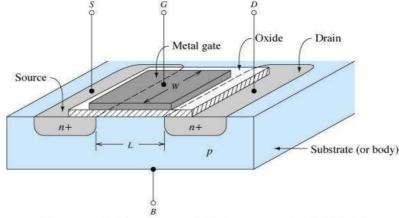

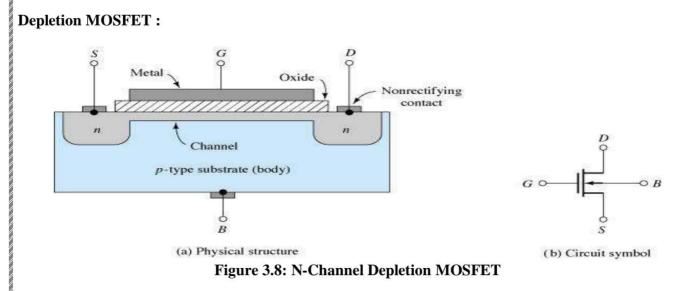

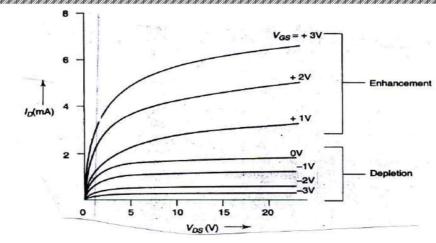

**BJT:** Junction transistor, transistor current components, transistor equation, transistor configurations, transistor as an amplifier, characteristics of transistor in Common Base, Common Emitter and Common Collector configurations, Ebers-Moll model of a transistor, punch through/ reach through, Photo transistor, typical transistor junction voltage values.**FET:** FET types, construction, operation, characteristics, parameters, MOSFET-types, construction, operation, characteristics, comparison between JFET and MOSFET.

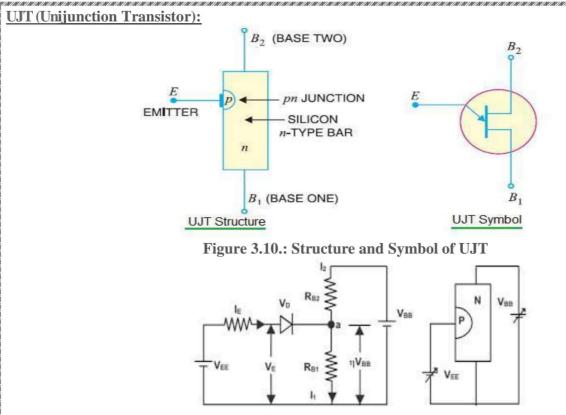

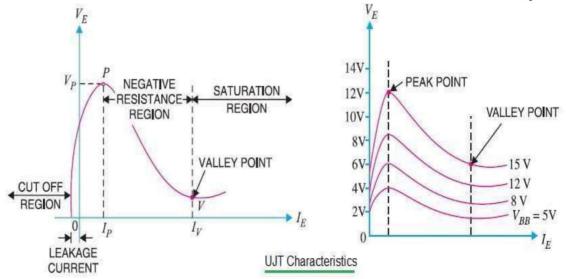

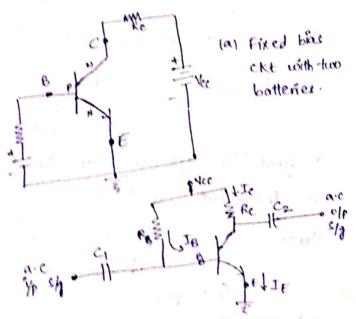

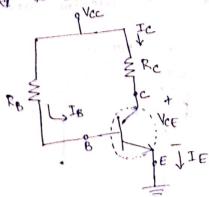

$$\begin{aligned} \begin{array}{c} \text{Transfitting} \\ \text{Unipoles Junchion Transister} \\ \text{CUIT?} \\ \end{array}{} \begin{array}{c} \text{Bipoler Junchion Transister} \\ \text{CUIT?} \\ \end{array}{} \begin{array}{c} \text{Bipoler Junchion Transister} \\ \text{CUIT?} \\ \end{array}{} \begin{array}{c} \text{Bipoler Junchion Transister} \\ \text{CUIT?} \\ \end{array}{} \begin{array}{c} \text{Unipole Junchion Transister is only \\ \text{migority converses.} \\ \end{array}{} \begin{array}{c} \text{The current conduction is only \\ \text{migority converses.} \\ \end{array}{} \begin{array}{c} \text{The current conduction is only \\ \text{migority converses.} \\ \end{array}{} \begin{array}{c} \text{The current conduction is only \\ \text{migority converses.} \\ \end{array}{} \begin{array}{c} \text{The current conduction Transister (BJT) \\ \end{array}{} \end{array}{} \end{array}{} \end{array}{} \begin{array}{c} \text{Unipole Junchion Transister (BJT) \\ \end{array}{} \end{array}{} \end{array}{} \end{array}{} \\ \begin{array}{c} \text{Construction Transister (BJT) \\ \end{array}{} \end{array}{} \end{array}{} \end{array}{} \end{array}{} \begin{array}{c} \text{The current conduction is biplow missing and majority converses.} \\ \end{array}{} \end{array}{} \end{array}{} \end{array}{} \end{array}{} \begin{array}{c} \text{Biplar Junchion Transister (BJT) \\ \end{array}{} \end{array}{} \end{array}{} \end{array}{} \end{array}{} \end{array}{} \begin{array}{c} \text{Construction Transister (BJT) \\ \end{array}{} \end{array}{} \end{array}{} \end{array}{} \end{array}{} \end{array}{}$$

\* The Emitter - Bake Junction is forward bian While The collector-Base Junction is Reverse bialo \* The majority comiers will flow from E to B across forward bian function.

- \* Because The Base layer is very thin 4 has a high resistance most of these carriers will dittuk across the remark black junction into the collector in the same direction of the minority charges 4 only tiny amount will flow out of the Back Terminal. of current

- \* Typically collector currents are of the order of mA While Base currents are MA.

- \* Applying Kirchhoff's current law:

\* The collector current is comprised of 2 components -> majority & minority \* The minority current component is called leatrage current, Ico (Ic with Emitter terminal open).

\* So the collector current is

Ic = Icmajority + Icominority

Transistor Configurations:

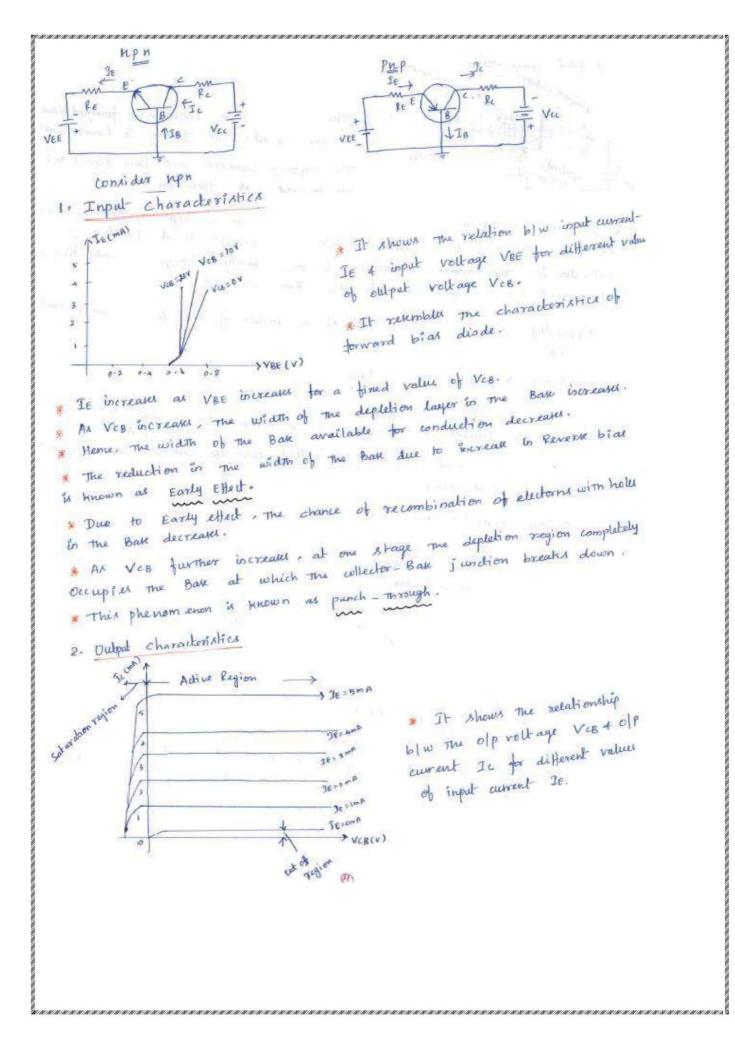

- 1. Common Bare (CB) configuration

- 2. common Emitter (CE) configuration

- 3. common collector (cc) configuration

- configuration 1. Common Bak

\* The Bake terminal is common to both ilp 4 elp. \* The ilp is applied blue The Emilter + the bake 4 ofp is taken collector 4 Barc. from

1) cut-off fegins

• Both the junctions are reverse black.

• When the excitor is le is zero.

• When the context is le is zero.

• When the context is le is zero.

• When the calledo-back junction is prevent black , the current due to minority converse flows from the collector to the back is represented at the context of the top the top the back of the collector-back junction is forward black of the collector-back junction of alchorn the top tractack a value large enough to ensure a large shown by heirowhal line.

• At 3E increases, it is increase.

10) Schwahim Regim

• Both junctions factor (A)

• The two ratio of change in collector current to the change in the top cannot of the change in the collector back veloce Ves.

Current Amplification factor (A)

• The two ratio of change in collector ensure to the change in the collector back of the collector back veloce Ves.

$$A_{AC} = \frac{A_{IE}}{A_{IB}} | ves = contact denset is the change is the collector back veloce Ves.

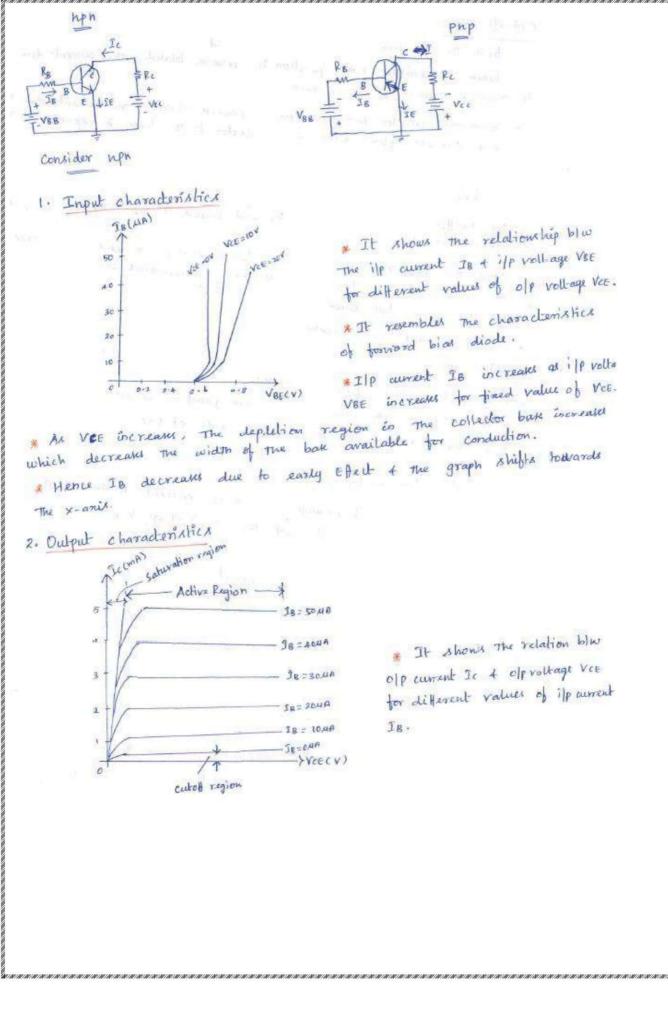

• Comment - Emilter conjeguration:

• Turput is applied by back of Emilter and output is black of the large is black of the by a collector of the by a collector of the by and the set of the set$$

- i) cut-off Region

- \* Both the junctions are remetrix biased.

- \* When the emitter base junction is reverse bialed, the current due to majority camera is IB is zero.

- \* When The collecto-back junction is reverse biased. The current due to minority carriers flows from The collector to emitter which is represented as ICEO.

- ii) Active Region

- \* The Emiller-base junction is forward blacked 4 The collector-base jurchie \* As IB is maintained constant, current Ic increases at revente-biate is reverse bialed.

- vellage Vee increases.

- iii) Saturation Region

- \* Both junctions are forward bland. \* When VEE is reduced to a small value such as 0.2 V. the collector ball jundion is actually forward blackd.

- \* It This region, There is a large change in Ic with small change En VEE

- current Amplification factor (B)

- \* It's defined as The change in collector current to the change in base current as constant collector-Emitter Vollage Vee.

$$\beta_{AC} = \frac{\Delta I_C}{\Delta I_B} |_{V \in E} = constant$$

\* It only be values are considered

$$B_{DC} = \frac{I_C}{T_B}$$

Relation between & and B

Also, Boc = Ic - @

From ()

$$IB = IE - Ic - (2)$$

Aub (3) in (2)  $\beta_{Dc} = \frac{Ic}{IE - Ic} - (2)$

\* Divide eqn @ by lebors Numerator 4 Denominator

@

$$\Rightarrow$$

$\beta_{De} = \frac{Te | Te}{\frac{Te}{Te} - \frac{Te}{Te}} = \frac{Te | IE}{1 - \frac{Te}{TE}} - @$

W H.T.  $K_{De} = \frac{Te}{TE}$

Sub  $\varkappa_{De}$  is eqn @

@  $\Rightarrow$   $\beta_{PE} = \frac{d_{DE}}{1 - d_{DE}}$

\*  $Tb$  subscript De is ignored

$\beta = \frac{\pi}{1 - d}$

Collector Current (Ie):

\* Apply Ket to the transistor

$Te = IB + Ie - @$

\* The collector current has 2 components

$Ie = I_{embjority} + I_{eminority}$

$Ie = Marie transistors  $\rightarrow$  Ie is measured in the 4 Ieo is

Weasured in Ala (co) nA.

Sub eq (D in @)

$Te = \pi (TB + Ie) + Iee$

$= \pi Te + \pi (IB + Ie) + Iee$

$= \pi Te + \pi Ie + \pi e^{-\pi}$

* For general purpose Transistors  $\rightarrow$  Ie is measured in the 4 Ieo is

Multer @ in @)

$Ie = \pi (IB + Ie) + Iee$

$= \pi Te + \pi Ie + \pi e^{-\pi}$

$Ie (1-\pi) = \pi IB + Ie^{-\pi}$

$Ie = \frac{\pi}{1-\pi} TB + \frac{1}{1-\pi} Teo$

$Ie = \frac{\pi}{1-\pi} (B+I) = 1e^{-\pi}$

$\beta IB + \frac{1}{1-\pi} Ie^{-\pi}$

$\beta IB + \frac{1}{1-\pi} Ie^{-\pi}$$

\*\*\*\*\*\*

ATT / ATT

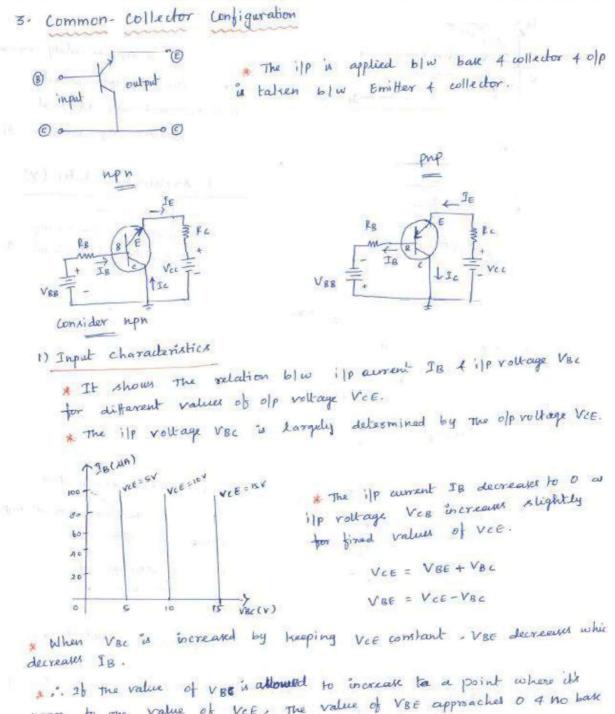

near to me value of VEE, The value of VBE approaches 0 4 no back current will flow.

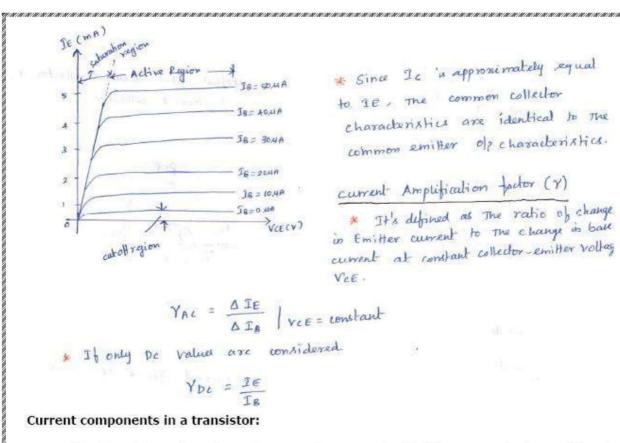

2) Output characteristics.

It shows the relation blue of purrent IE + of prollage Vec for different values of ilp aurent IB.

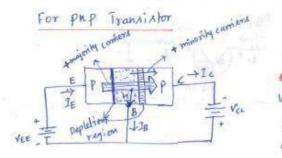

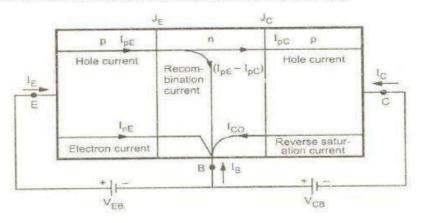

The figure below shows the various current components which flow across the forward-biased emitter junction and reverse-biased collector junction in P-N-P transistor.

Figure. Current components in a transistor with forward-biased emitter and reverse-biased collector junctions.

The emitter current consists of the following two parts:

- Hole current IpE constituted by holes (holes crossing from emitter into base).

- 4. Electron current InE constituted by electrons (electrons crossing from base into the emitter).

Therefore, Total emitter current  $I_E = I_{pE}$  (majority)+  $I_{nE}$  (Minority)

The holes crossing the emitter base junction  $J_E$  and reaching the collector base junction  $J_C$  constitutes collector current  $I_{pC}$ .

Not all the holes crossing the emitter base junction  $J_E$  reach collector base junction  $J_C$  because some of them combine with the electrons in the n-type base.

Since base width is very small, most of the holes cross the collector base junction  $J_C$  and very few recombine, constituting the base current ( $I_{pE} - I_{pC}$ ).

When the emitter is open-circuited,  $I_E=0$ , and hence  $I_{pC}=0$ . Under this condition, the base and collector together current  $I_C$  equals the reverse saturation current  $I_{CO}$ , which consists of the following two parts:  $I_{PCO}$  caused by holes moving across  $I_C$  from N-region to P-region.

$I_{nCO}$  caused by electrons moving across  $I_C$  from P-region to N-region.  $I_{CO} = I_{nCO} + I_{PCO}$ In general,  $I_C = I_{nC} + I_{PC}$

Thus for a P-N-P transistor,  $I_E = I_B + I_C$

Ebers-

### FIELD EFFECT TRANSISTOR:

FET is a device in which the flow of current through the conducting region is controlled by an electric field. Hence the name Field Effect Transistor (FET). As current conduction is only by majority carriers, FET is said to be a unipolar device.

Based on the construction, the FET can be classified into two types as Junction FET (JFET) and Metal Oxide Semiconductor FET(MOSFET).

Depending upon the majority carriers, JFET has been classified into two types named as (1) Nchannel JFET with electrons as the majority carriers and (2) P-channel JFET with holes as the majority carriers.

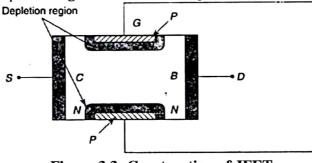

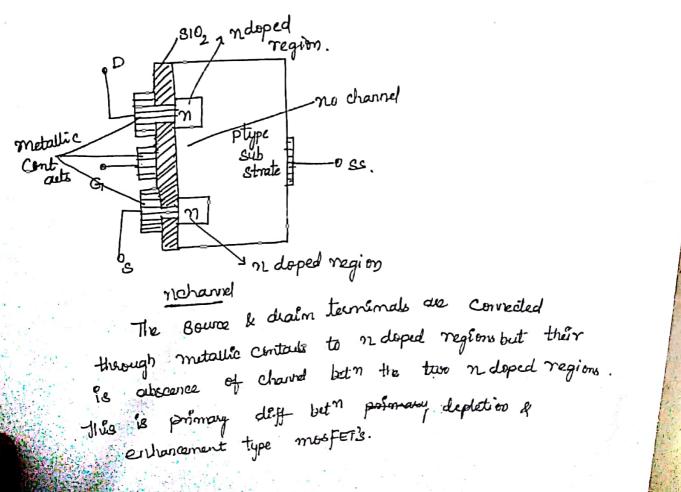

#### **Construction of N-Channel JFET :**

It consists of an N-type bar which is made of silicon. Ohmic contacts, (terminals) made at the two ends of the bar, are called Source and Drain.

Source (S) This terminal is connected to the negative pole of the battery. Electrons which are the majority carriers in the N-type bar enter the bar through this terminal.

Drain (D) This terminal is connected to the positive pole of the battery. The majority carriers leave the bar through this terminal.

Gate (G) Heavily doped P-type silicon is diffused on both sides of the N-type silicon bar by which PN junctions are formed. These layers are joined together and called Gate G.

*Channel* The region BC of the N-type bar in the depletion region is called the channel. Majority carriers move from the source to drain when a potential difference  $V_{DS}$  is applied between the source and drain.

#### **Operation of N-channel JFET:**

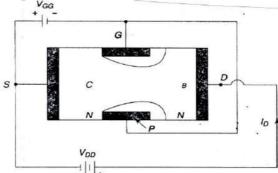

When  $V_{GS} = 0$  and  $V_{DS} = 0$  When no voltage is applied between drain and source, and gate and source, the thickness of the depletion regions around the PN junction is uniform as shown in figure.

**Figure 3.3: Construction of JFET**

When  $V_{DS} = 0$  and  $V_{GS}$  is decreased from zero. In this case PN junctions are reverse biased and hence the thickness of the depletion region increases. As  $V_{GS}$  is decreased from zero, the reverse bias voltage across the PN junction is increased and hence the thickness of the depletion region in the channel increases until the two depletion regions make contact with each other. In this condition, the channel is said to be cutoff. The value of  $V_{GS}$  which is required to cutoff the channel is called the cutoff voltage  $V_C$ .

When  $V_{GS} = 0$  and  $V_{DS}$  is increased from zero. Drain is positive with respect to the source with  $V_{GS} = 0$ . Now the majority carriers (electrons) flow through the N-channel from source to drain. Therefore the

conventional current  $I_D$  flows from drain to source. The magnitude of the current will depend upon the following factors:-

- 1. The number of the majority carriers (electrons) available in the channel, i.e. the conductivity of the channel.

- 2. The length l of the channel.

- 3. The cross sectional area *A* of the channel at *B*.

- 4. The magnitude of the applied voltage  $V_{DS}$ . Thus the channel acts as a resistor of resistance R given by

$$R = \frac{\rho I}{A} \qquad \dots (1)$$

$$I_{D} = \frac{V_{DS}}{R} = \frac{A V_{DS}}{\rho I} \qquad \dots (2)$$

where  $\rho$  is the resistivity of the channel. Because of the resistance of the channel and the applied voltage V<sub>DS</sub>, there is a gradual increase of positive potential along the channel from source to drain. Thus the reverse voltage across the PN junctions increases and hence the thickness of the depletion regions also increases. Therefore the channel is wedge shaped, as shown in figure.

Figure 3.4: JFET under applied bias

As  $V_{DS}$  is increased, the cross-sectional area of the channel will be reduced. At a certain value  $V_P$  of  $V_{DS}$ , the cross-sectional area at B becomes minimum. At this voltage, the channel is said to be pinched off and the drain voltage  $V_P$  is called the pinch-off voltage.

As a result of the decreasing cross-section of the channel with the increase of  $V_{DS}$ , the following results are obtained.

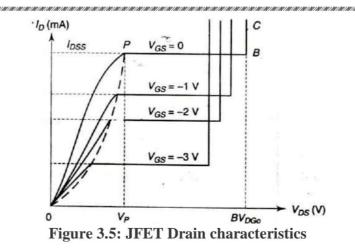

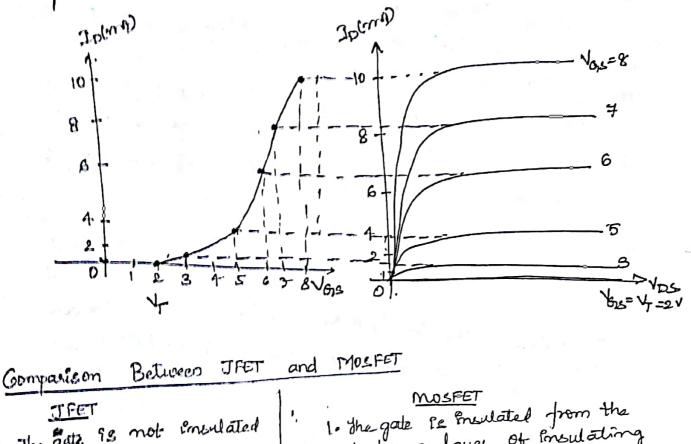

- (i) As  $V_{DS}$  is increased from zero,  $I_D$  increases along OP, and the rate of increase of  $I_D$  with  $V_{DS}$  decreases as shown in figure.

- (ii) When  $V_{DS} = V_P$ ,  $I_D$  becomes maximum. When  $V_{DS}$  is increased beyond  $V_P$ , the length of the pinch-off region increases. Hence there is no further increase of  $I_D$ .

- (iii) At a certain voltage corresponding to the point B,  $I_D$  suddenly increases. This effect is due to the avalanche multiplication of electrons caused by breaking of covalent bonds of silicon atoms in the depletion region between the gate and the drain. The drain voltage at which the breakdown occurs is denoted by  $BV_{DGO}$ . The variation of  $I_D$  with  $V_{DS}$  when  $V_{GS} = 0$  is shown in figure by the curve OPBC.

When  $V_{GS}$  is negative and  $V_{DS}$  is increased. When the gate is maintained at a negative voltage less than the negative cutoff voltage, the reverse voltage across the junction is further increased. Hence for a negative value of  $V_{GS}$ , the curve of  $I_D$  versus  $V_{DS}$  is similar to that for  $V_{GS} = 0$ , but the values of  $V_P$  and  $BV_{DGO}$  are lower, as shown in figure.

From the curves, it is seen that above the pinch-off voltage, at a constant value of  $V_{DS}$ . I<sub>D</sub> increases with an increase of  $V_{GS}$ . Hence a JFET is suitable for use as a voltage amplifier, similar to a transistor amplifier.

It can be seen from the curve that for the voltage  $V_{DS} = V_P$ , the drain current is not reduced to zero. If the drain current is to be reduced to zero, the ohmic voltage drop along the channel should also be reduced to zero. Further, the reverse biasing to the gate-source PN junction essential for pinching off the channel would also be absent.

The drain current  $I_D$  is controlled by the electric field that extends into the channel due to reverse biased voltage applied to the gate; hence this device has been given the name "Field Effect Transistor".